芯片封装早已不再仅限于传统意义上为独立芯片提供保护和I/O扩展接口,如今有越来越多的封装技术能够实现多种不同芯片之间的互联。先进封装工艺能提高器件密度并由此减小空间占用,这一点对于手机和自动驾驶汽车等电子设备的功能叠加来说至关重要。芯片封装行业的发展使国际电气电子工程师协会电子元件封装和生产技术学会(IEEE-CPMT)意识到必须要拓展自身的技术范畴,并于2017年正式更名为国际电气电子工程师协会电子封装学会(IEEE- EPS)。

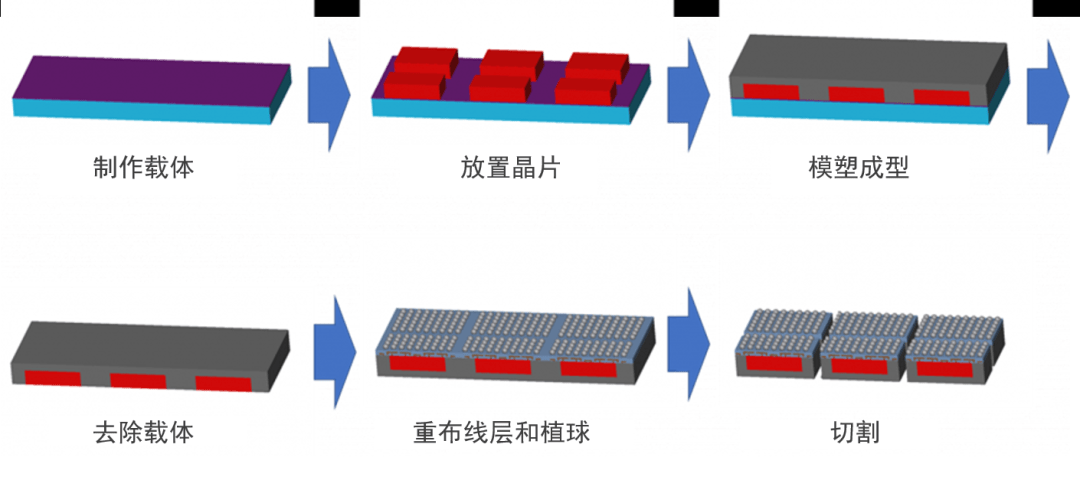

有一种先进封装技术被称为“晶圆级封装”(WLP),即直接在晶圆上完成集成电路的封装程序。通过该工艺进行封装,可以制成与原裸片大小近乎相同的晶圆。早在2000年代末,英飞凌开发的嵌入式晶圆级球栅阵列(eWLB)就是一种晶圆级封装技术。目前有许多封测代工厂(OSAT)都在使用eWLB的变种工艺。具体来说,eWLB封装是指将检验合格的晶片正面朝下,放置在载体晶圆上并将两者作为整体嵌入环氧树脂模具。在模铸重构晶片结构之后进行“扇出型”封装,在暴露的晶圆表面进行重布线层工艺(RDLs)并植球,之后再将其切割成小块即可获得可供使用的芯片(图1)。

图1 eWLB封装流程

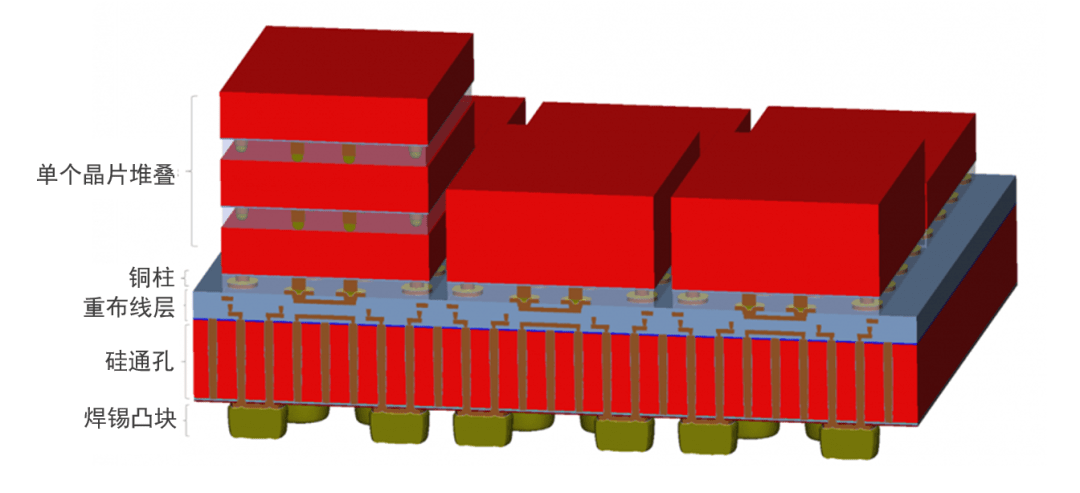

图2展示的是其他结合晶圆级封装的综合性先进封装技术。

硅通孔技术(TSV)是指完全穿透硅基底的垂直互连。图2展示的是基于硅中介层的硅通孔技术,即通过硅中介层实现高密度晶片与封装层之间的电气连接。该技术起初作为打线接合的替代方法而备受推广,能够在减小互联长度来优化电阻的同时,通过多个晶片堆叠实现3D集成。

图2 器件封装示意图

作为导电互联技术的应用,重布线层的作用是重新分布连接至晶片焊盘I/O点位的电子线路,并且可以放置在单个晶片的一侧或两侧。随着对带宽和I/O点位需求的提升,重布线层的线宽和间距也需要不断缩小。为了满足这些要求,目前工艺上已采用类似后段制程的铜镶嵌技术来减小线宽,并通过铜柱代替传统焊接凸点的方法来减小晶片间连接的间距。

先进封装技术还在持续发展,以满足不断提升的器件密度和I/O连接性能要求。近几年出现的铜混合键合技术就是很好的例子,它的作用是直接将一个表面的铜凸点和电介质连接至另一个主动表面的相应区域,由此规避对凸点间距的限制。我们非常期待这些封装技术上的创新能够引领新一代电子产品的稳步发展。